TOKYO — (BUSINESS WIRE) — February 26, 2019 — Toshiba Electronic Devices & Storage Corporation (“Toshiba”) today announced development of an image recognition SoC (System on Chip) for automotive applications that implements deep learning accelerator at 10 times the speed and 4 times the power efficiency of Toshiba’s previous product[1]. Details of the technology were reported at the 2019 IEEE International Solid-State Circuits Conference (ISSCC) in San Francisco on February 19.

This press release features multimedia. View the full release here: https://www.businesswire.com/news/home/20190226005488/en/

Toshiba: DNN Accelerator (Graphic: Business Wire)

Advanced driver assistance systems, such as autonomous emergency braking, offer increasingly advanced capabilities, and implementing them requires image recognition SoC that can recognize road traffic signs and road situations at high speed with low power consumption.

Deep neural networks (DNN), algorithms modeled after the neural networks of the brain, perform recognition processing much more accurately than conventional pattern recognition and machine learning, and are widely expected to find utilization in automotive applications. However, DNN-based image recognition with conventional processors takes time, as it relies on a huge number of multiply-accumulate (MAC) calculations. DNN with conventional high-speed processors also consumes too much power.

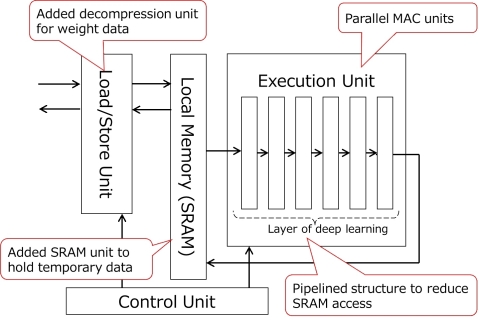

Toshiba has overcome this with a DNN accelerator that implements deep learning in hardware. It has three features.

- Parallel MAC units. DNN processing requires many MAC computations. Toshiba’s new device has four processors, each with 256 MAC units. This boosts DNN processing speed.

- Reduced DRAM access. Conventional SoC have no local memory to keep temporal data close to the DNN execution unit and consume a lot of power accessing local memory. Power is also consumed loading the weight data, used for the MAC calculations. In Toshiba’s new device, SRAM are implemented close to the DNN execution unit, and DNN processing is divided into sub-processing blocks to keep temporal data in the SRAM, reducing DRAM access. Additionally, Toshiba has added a decompression unit to the accelerator. Weight data, compressed and stored in DRAM in advance, are loaded through the decompression unit. This reduces the power consumption involved in loading weight data from DRAM.

- Reduced SRAM access. Conventional deep learning needs to access SRAM after processing each layer of DNN, which consumes too much power. The accelerator has a pipelined layer structure in the DNN execution unit of DNN, allowing a series of DNN calculations to be executed by one SRAM access.

The new SoC complies with ISO26262, the global standard for functional safety for automotive applications.

Toshiba will continue to enhance the power efficiency and processing speed of the developed SoC and will start sample shipments of ViscontiTM5, the next generation of Toshiba’s image-recognition processor, in September this year.

|

Notes |

||

| [1] | Toshiba’s image recognition SoC in “1.9TOPS and 564GOPS/W Heterogeneous Multicore SoC with Color-based Object Classification Accelerator for Image-Recognition Applications,” a paper delivered at the 2015 IEEE International Solid-State Circuits Conference | |

* ViscontiTM is a trademark of Toshiba Electronic Devices &

Storage Corporation

* All other company names, product names and

service names may be trademarks of their respective companies.

About Toshiba Electronic Devices & Storage Corporation

Toshiba Electronic Devices & Storage Corporation combines the vigor of a new company with the wisdom of experience. Since becoming an independent company in July 2017, we have taken our place among the leading general devices companies, and offer our customers and business partners outstanding solutions in discrete semiconductors, system LSIs and HDD.

Our 22,000 employees around the world share a determination to maximize

the value of our products, and emphasize close collaboration with

customers to promote co-creation of value and new markets. We look

forward to building on annual sales now surpassing 800-billion yen (US$7

billion) and to contributing to a better future for people everywhere.

Find

out more about us at

https://toshiba.semicon-storage.com/ap-en/top.html

View source version on businesswire.com: https://www.businesswire.com/news/home/20190226005488/en/

Contact:

Media Inquiries:

Toshiba Electronic Devices & Storage

Corporation

Business Planning Div. Public Relations & Investor

Relations Group

Motohiro Ajioka

Tel: +81-3-3457-3576

Email Contact