Hsinchu, Taiwan and San Jose, Calif., Dec. 05, 2019 (GLOBE NEWSWIRE) -- Andes Technology Corporation, the world leader in RISC-V CPU solutions, announces AndesCore™ 45-series CPU cores today. It is equipped with efficient superscalar pipeline to address a wide range of high-performance, power-sensitive and real-time embedded systems such as 5G, In-Vehicle Infotainment (IVI), Advanced Driver Assistance Systems (ADAS) and Solid State Disks (SSD). Availability of the CPU cores to early adopted customers is scheduled from Q1, 2020.

High-performance embedded systems have come to the fork of the road. On one hand, customers have enjoyed the ecosystem of industry successful processors. But they crave the freedom to go beyond the fixed instructions and microarchitecture platforms. The AndesCore 45-series is specifically designed to provide such solution.

“The 45-series is an important milestone to high-performance space for Andes, this time with the RISC-V instruction set and all the momentum that comes with it,” said Andes President, Frankwell Lin. “Our licensees have asked us to bring our dual-issue processor expertise to the RISC-V cores, and I am glad our R&D team has come through again.”

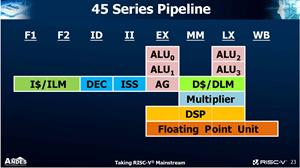

Initially available in the 45-series will be the 32-bit A45/D45/N45 and 64-bit AX45/DX45/NX45, which benefit from Andes proven 25-series cores, respectively, supporting all of latest RISC-V specifications, subsystem level components, as well as ecosystem enablement from Andes’ 14-years of R&D development. The A-prefix supports Linux and scales up to four cores, N-prefix supports RTOS, while D-prefix supports RISC-V packed SIMD/DSP instructions (P-extension draft). All 45-series cores employ in-order, 8-stage, dual-issue superscalar with careful memory pipeline designs to incorporate ECC without sacrificing clock speed, and the IEEE754-compliance single and double precision Floating Point Unit (FPU) could be selected. Indeed, the AX45 core can deliver 1.2GHz at 28nm worst case PVT corner with ECC turned on, making it one of the most robust pipeline designs at this performance level. The vastly superior pipelining also results in world-class 5.4 Coremark/MHz. These cores are in-order processors to enhance real-time determinism for code execution. When coupled with Andes Platform-Level-Interrupt-Controller (PLIC) with priority-based preemption, the 45-series cores are ideal for embedded applications where response times and determinism are critical.

The 45-series cores continue AndesCore™ strong heritage for rich processor subsystem design, starting with memory subsystem with local memory support and configurable instruction & data caches of varying sizes, and associativity. Advanced branch prediction further improves processor performance with minimal power consumed. Memory Management Unit (MMU) with configurable table sizes enables the A-prefix 45-series family to run Linux operating systems now fully supported in RISC-V community. Most importantly, the 45-series family will be released with all of Andes existing RISC-V ecosystem partner solutions already enabled, from security solutions to system level modeling, and hardware debug/trace subsystems.

“While it’s gratifying to bring our years of high-performance processor experience to the 45-series RISC-V product family, it’s the ecosystem, partnership, and market momentum that’s truly exciting.” said Dr. Charlie Su. “A fast processor is nice, but partners and licensees trust us because we have delivered differentiated features, solutions, and enablement supports to help them get to revenue quickly.”

As with Andes 25-series family of processor cores now in production for two years, the 45-series family will support all existing Andes features such as PowerBrake, QuickNap™, WFI for additional power saving; StackSafe™ for stack overflow/underflow protection; CoDense™ for additional code density enhancement beyond RISC-V C-extension; and Andes Custom Extension™ (ACE) for user-defined instructions to realize domain-specific architecture.

Pricing and Availability:

The 45-series family of cores will be available to early licensees from Q1, 2020. Please contact Andes Sales at

sales@andestech.com for configuration and pricing of the 45-series processors.

About Andes Technology

Fourteen years after starting from scratch, Andes Technology Corporation is now a world class creator of innovative high-performance/low-power 32/64-bit processor cores and associated development environment that serves the rapidly growing global market for embedded system applications. A founding Platinum member of RISC-V Foundation, Andes is the first mainstream CPU vendor that has adopted the RISC-V as the base of its fifth-generation architecture, the AndeStar™ V5. To meet the demanding requirements of today's electronic devices, Andes delivers highly configurable and performance-efficient CPU cores with full-featured integrated development environment and comprehensive software/hardware solutions to help customers innovate their SoC in a shorter time to market. Since 2018, the yearly volume of SoCs Embedded with Andes CPUs has surpassed the 1-billion mark. Andes Technology's comprehensive RISC-V CPU families range from the entry-level N22 (32-bit only) and mid-range 25-series, to the newly announced advanced 27-series and 45-series.

For more information, please visit https://www.andestech.com

Attachment

Hsiao-Ling Lin +886 912-032-463 hllin@andestech.com Jonah McLeod +1 (510) 449-8634 Jonahm@andestch.com