"The demand for custom SoCs in the era of pervasive intelligence requires extensive ecosystem collaboration to help customers accelerate their innovation and silicon success on Samsung's SF2 and next-generation SF1.4 processes," said Sanjay Bali, vice president of product management and strategy for the EDA Group at Synopsys. "Achieving certification and multiple successful tapeouts of our digital and analog flows, powered by Synopsys.ai, on the SF2 process, combined with proven Synopsys IP provides designers with a trusted path to meeting their aggressive design goals for a faster time to market."

"Synopsys and Samsung have worked closely for decades to help our mutual customers achieve their most complex design requirements," said Sangyun Kim, Vice President and head of Foundry Design Technology Team at Samsung Electronics. "This latest collaboration milestone with Synopsys on AI-driven EDA flows and broad IP portfolio development is a testament to our ongoing efforts to address the industry's growing demand for high performance computing with significant PPA gains. Working together we validated our PPA results using Synopsys' certified digital flow, achieving 12% higher performance, 25% reduction in power, and 5% area reduction compared to the base design."

Collaboration on AI-driven EDA Flows

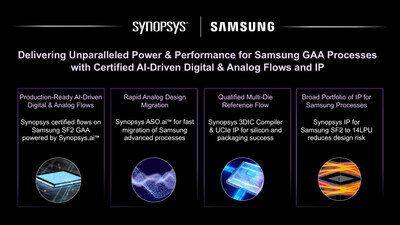

Synopsys and Samsung are closely collaborating on AI-driven flows, including

Synopsys DSO.ai™ for design productivity and PPA optimization, and

Synopsys ASO.ai™ for faster analog design migration. This collaboration has resulted in a new analog design migration reference flow using Synopsys ASO.ai for Samsung's FinFET to GAA processes, enabling designers to efficiently migrate Samsung 8nm analog IPs to SF2 process, adding to Synopsys' established flows on Samsung's 14nm to 8nm/SF5 processes.

New Design Techniques and Methodology for Advanced GAA Processes

Synopsys' continued innovation helps mutual customers benefit from new design techniques including backside routing, local layout effect-aware methodology, and nanosheet cell design, to help customers meet their design goals for power, performance, and area on Samsung SF2 process family. In addition, integrating backside routing and the super-cell approach using Synopsys' digital implementation and signoff tools enables designers to increase transistor performance efficiency and density, optimize power consumption, and reduce area by up to 20% for Samsung's SF2Z process technology compared to chips without backside routing capabilities.

Accelerate SoC and Multi-Die Designs

Synopsys IP for Samsung standard and automotive processes from SF2 to SF14LPU delivers a competitive edge for chipmakers looking to reduce integration risk and accelerate time to silicon success for automotive, mobile, high-performance computing (HPC) and multi-die designs. The industry's broadest portfolio of standards-compliant, silicon-proven interface IP for advanced Samsung processes, including PCIe 6.0/5.0/4.0, DDR5, LPDDR5X/5/4X, MIPI M-PHY G5, eUSB2, USB 3.2/3.1, and DisplayPort enables wide interoperability for commonly used protocols. To accelerate integration of chiplets in multi-die packages, Synopsys UCIe IP has taped out in SF2 and SF4x, and achieved silicon success in SF5A process technologies, to deliver robust die-to-die connectivity with low power and low latency. Synopsys Foundation IP, including embedded memories, logic libraries and GPIOs, is also proven in silicon to deliver leading power, performance, and area in a range of Samsung process technologies.

Mutual customers can accelerate the development of multi-die designs using Synopsys 3DIC Compiler, a unified exploration-to-signoff platform for 2.5D and 3D heterogeneous integration and advanced packaging. Qualified for Samsung Foundry's SF2 process, Synopsys 3DIC Compiler supports Samsung's advanced silicon processes, packaging technologies, and 3DCODE standard. Synopsys is an active member of the Samsung Foundries' MDI Alliance, helping mutual customers achieve a successful transition to 2.5D and 3D advanced packaging designs.

About Synopsys

Catalyzing the era of pervasive intelligence, Synopsys, Inc. (Nasdaq:

SNPS) delivers trusted and comprehensive silicon to systems design solutions, from electronic design automation to silicon IP and system verification and validation. We partner closely with semiconductor and systems customers across a wide range of industries to maximize their R&D capability and productivity, powering innovation today that ignites the ingenuity of tomorrow. Learn more at

www.synopsys.com.

Editorial Contact

Kelli Wheeler

Synopsys, Inc.

(650) 584-5000

Email Contact

Email Contact

![]() View original content to download multimedia:

https://www.prnewswire.com/news-releases/synopsys-achieves-certification-of-its-ai-driven-digital-and-analog-flows-and-ip-on-samsung-advanced-sf2-gaa-process-302171192.html

View original content to download multimedia:

https://www.prnewswire.com/news-releases/synopsys-achieves-certification-of-its-ai-driven-digital-and-analog-flows-and-ip-on-samsung-advanced-sf2-gaa-process-302171192.html

SOURCE Synopsys, Inc.

| Contact: |

| Company Name: Synopsys, Inc.

Financial data for Synopsys, Inc. |