DesignWare Logic Library, Embedded Memory, Interface, and Analog IP on TSMC 16FFC Cuts Power Consumption for Advanced SoCs

MOUNTAIN VIEW, Calif., March 14, 2016 — (PRNewswire) —Highlights:

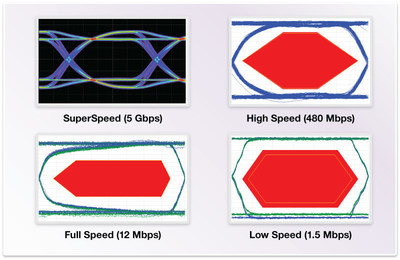

- DesignWare interface and analog IP portfolio for TSMC 16FFC process includes USB 3.1/3.0/2.0, USB Type C 3.1/DisplayPort 1.3, DDR4/3, LPDDR4, PCI Express 4.0/3.1/2.1, SATA 6G, HDMI 2.0, MIPI M-PHY and D-PHY, and data converters

- High-speed, high-density and ultra-high-density logic libraries, memory compilers and High-Performance Core Design Kits deliver superior performance, power and area on TSMC 16FFC

- STAR Memory System® provides efficient diagnostics and repair of FinFET-based memories, while STAR Hierarchical System automates hierarchical testing for SoCs

Synopsys, Inc. (Nasdaq: SNPS) today announced a broad IP portfolio for TSMC's 16-nanometer FinFET Compact (16FFC) process for reliable integration into cost-sensitive, ultra-low power applications including mobile, Internet of Things (IoT), digital home and automotive. Synopsys DesignWare® IP on the 16FFC process enables designers to accelerate development of SoCs that incorporate logic libraries, embedded memories, embedded test and repair, USB 3.1/3.0/2.0, USB-C 3.1/DisplayPort 1.3, DDR4/3, LPDDR4, PCI Express® 4.0/3.1/2.1, SATA 6G, HDMI 2.0, MIPI M-PHY and D-PHY and data converter IP.

"The 16FFC process reduces SoC power consumption by more than 50 percent (at the same frequency) compared to the 28HPM process and optimizes die area to lower system cost. Synopsys' DesignWare IP portfolio for the TSMC 16FFC process helps our mutual customers achieve their SoC performance, power and area targets," said Suk Lee, TSMC senior director, Design Infrastructure Marketing Division. "Synopsys continues to provide proven IP solutions that support TSMC's latest process technologies, helping designers achieve their time-to-market objectives."

"Synopsys' broad portfolio of high-quality IP on the 16FFC process is another significant milestone in our successful history of providing silicon-proven IP in advanced FinFET processes," said John Koeter, vice president of marketing for IP and prototyping at Synopsys. "With a complete, low-power solution including Synopsys PHY IP on the TSMC 16FFC process and digital interface controller IP that supports the IEEE 1801-2009 Unified Power Format, designers can reduce SoC power consumption and extend battery life for smart phones, consumer products and wearables."

Availability

The DesignWare Logic Libraries and DDR4/3 PHYs are available now for TSMC 16FFC. DesignWare USB 3.1/3.0/2.0 PHYs, HDMI 2.0 PHYs and MIPI D-PHY design kits are available in March 2016.

The DesignWare Memory Compilers, STAR Memory System and STAR Hierarchical System® solutions, PCI Express 4.0/3.1/2.1 PHYs, SATA 6G PHYs, MIPI M-PHY, USB-C 3.1/DisplayPort 1.3 PHYs, LPDDR4 PHYs and data converter IP design kits are scheduled to be available for TSMC 16FFC in Q2 2016.

About DesignWare IP

Synopsys is a leading provider of high-quality, silicon-proven IP solutions for SoC designs. The broad DesignWare IP portfolio includes logic libraries, embedded memories, embedded test, analog IP, wired and wireless interface IP, security IP, embedded processors and subsystems. To accelerate prototyping, software development and integration of IP into SoCs, Synopsys' IP Accelerated initiative offers IP prototyping kits, IP software development kits and IP subsystems. Synopsys' extensive investment in IP quality, comprehensive technical support and robust IP development methodology enables designers to reduce integration risk and accelerate time-to-market. For more information on DesignWare IP, visit http://www.synopsys.com/designware.

About Synopsys

Synopsys, Inc. (Nasdaq: SNPS) is the Silicon to Software™ partner for innovative companies developing the electronic products and software applications we rely on every day. As the world's 16th largest software company, Synopsys has a long history of being a global leader in electronic design automation (EDA) and semiconductor IP and is also growing its leadership in software quality and security solutions. Whether you're a system-on-chip (SoC) designer creating advanced semiconductors, or a software developer writing applications that require the highest quality and security, Synopsys has the solutions needed to deliver innovative, high-quality, secure products. Learn more at www.synopsys.com.

Forward-Looking Statements

This press release contains forward-looking statements within the meaning of Section 21E of the Securities Exchange Act of 1934, including statements regarding the expected release and benefits of the DesignWare USB-C 3.1/DisplayPort 1.3 PHYs, DDR4/3 PHYs, LPDDR4 PHYs and data converter IP for 16FFC. Any statements that are not statements of historical fact may be deemed to be forward-looking statements. These statements involve known and unknown risks, uncertainties and other factors that could cause actual results, time frames or achievements to differ materially from those expressed or implied in the forward-looking statements. Other risks and uncertainties that may apply are set forth in the "Risk Factors" section of Synopsys' most recently filed Annual Report on Form 10-K. Synopsys undertakes no obligation to update publicly any forward-looking statements, or to update the reasons actual results could differ materially from those anticipated in these forward-looking statements, even if new information

Editorial Contacts:

Monica Marmie

Synopsys, Inc.

650-584-2890

Email Contact

Photo- http://photos.prnewswire.com/prnh/20160310/342970

To view the original version on PR Newswire, visit: http://www.prnewswire.com/news-releases/synopsys-announces-broad-ip-portfolio-for-tsmc-16ffc-process-300234366.html

SOURCE Synopsys, Inc.

| Contact: |

| Synopsys, Inc.

Web: http://www.synopsys.com |