New release is a major step to achieving C++/SystemC signoff.

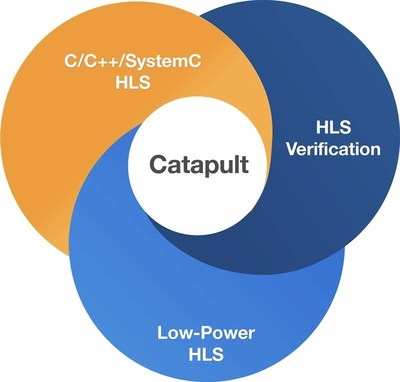

WILSONVILLE, Ore., June 2, 2016 — (PRNewswire) — Mentor Graphics Corporation (NASDAQ: MENT) today announced the latest release of the Catapult® Platform that decreases the hardware design time from the design start to register transfer level (RTL) verification closure by 50 percent compared to traditional hand-coded RTL. Existing High-Level Synthesis (HLS) methodologies improve design and verification productivity up to 10X; however, the time required to close verification on the resulting RTL can potentially wipe out these gains. This release of the Catapult Platform unifies HLS with a proven verification methodology and new tools that enable rapid and predictable RTL verification closure based on C++/SystemC-level verification closure—a major step toward C++/SystemC signoff.

NVIDIA® reports on their HLS design and verification success in the recent case study entitled Working Smarter, Not Harder: NVIDIA Closes Design Complexity Gap with High-Level Synthesis. "By adopting a C++ High-Level synthesis (HLS) flow using Catapult from Mentor Graphics, NVIDIA was able to simplify their code by 5X, reduce the number of CPUs required for regression testing by 1000X, and run 1000X more tests to achieve higher functional coverage of their designs. HLS decreased design time by 50 percent…" write authors Frans Sijstermans and JC Li. "The success of the video team's application of HLS resulted in its adoption company-wide for all new NVIDIA designs. When it comes to working smarter, not harder, HLS is the way to go."

Industry-first HLS (C++/SystemC) formal property checker

This latest Catapult release introduces an industry first, the Catapult formal-based C Property Checker (CPC) tool, which automatically finds bugs prior to synthesis, saving days or weeks of verification debugging time. CPC uses formal analysis to automatically identify and formally prove hard-to-find issues like uninitialized memory, divide by 0, and array bounds errors in the users' HLS C++/SystemC model (HLSM). In addition to automatic checks, CPC also formally prove user-written assertions and cover points which complement dynamic simulation providing comprehensive verification of the HLSM.

100 percent RTL coverage faster

The latest Catapult release also facilitates easier, faster and more predictable RTL verification closure. It achieves this by removing RTL redundancies, adding new RTL test pins, and synthesizing user assertions and cover points in the HLSM into SVA (SystemVerilog Assertions). To reach functional coverage closure more quickly, Catapult also generates a complete RTL test environment that re-uses the user's C++/SystemC testbench comparing to the original HLSM, to automatically verify that the simulation results are equivalent. To achieve 100 percent RTL structural/code coverage more quickly, Catapult works with the

Questa® CoverCheck tool in a seamless flow to quickly find and automatically generate waivers for unreachable code that can be safely ignored. For reachable code, the flow enables the user to quickly understand in generated waveforms what is needed for the HLSM to quickly close any remaining holes. This methodology enables verification to reach 100 percent RTL coverage closure in days after the HLSM is verified.

Enabling HLS standards and ecosystem

This release of Catapult HLS advances the standardization of the HLSM language by fully supporting the new Accellera SystemC Synthesizable Subset. In addition, Catapult supports Algorithmic C (AC) Datatypes for arbitrary-length, bit-accurate integers and fixed-point datatypes which provide static bit-precision and fast simulation time needed for both formal and dynamic tools. Mentor has now made

AC Datatypes open source and 100% compatible with the SystemC Synthesis standard. Mentor will also be donating them to Accellera for standardization.

HLS Vision of C++/SystemC sign-off

"With increased pressure to deliver more functionality with fewer resources, it is imperative that the design flow change to achieve substantially more productivity," said Badru Agarwala, Mentor Graphics General Manager, Calypto Systems Division. "Our vision is the completion of the HLS ecosystem, giving RTL designers the tools and methodologies they are familiar with to enable them to move to SystemC/C++ signoff. Achieving 100 percent RTL coverage, the HLS standards, and the industry first C++/SystemC formal property tool are major steps towards that vision."

About Mentor Graphics

Mentor Graphics Corporation is a world leader in electronic hardware and software design solutions, providing products, consulting services and award-winning support for the world's most successful electronic, semiconductor and systems companies. Established in 1981, the company reported revenues in the last fiscal year of approximately $1.18 billion. Corporate headquarters are located at 8005 S.W. Boeckman Road, Wilsonville, Oregon 97070-7777. Website: http://www.mentor.com

|

For more information, please contact: David Smith Mentor Graphics 503.685.1135 david_smith@mentor.com | |

|

|

|

Mentor Graphics, Catapult and Questa are registered trademarks of Mentor Graphics Corporation. All other company or product names are the registered trademarks or trademarks of their respective owners.

Photo - http://photos.prnewswire.com/prnh/20160601/374600

Logo - http://photos.prnewswire.com/prnh/20140317/AQ83812LOGO

To view the original version on PR Newswire, visit: http://www.prnewswire.com/news-releases/mentor-graphics-catapult-platform-cuts-overall-time-from-design-start-to-verification-closure-by-50-percent-300278479.html

SOURCE Mentor Graphics

| Contact: |

| Mentor Graphics

Web: http://www.mentor.com |